www.afm-iournal.de

## Gate Capacitance-Dependent Field-Effect Mobility in Solution-Processed Oxide Semiconductor Thin-Film **Transistors**

Eungkyu Lee, Jieun Ko, Keon-Hee Lim, Kyongjun Kim, Si Yun Park, Jae M. Myoung, and Youn Sang Kim\*

Solution-processed oxide semiconductors (OSs) used as channel layer have been presented as a solution to the demand for flexible, cheap, and transparent thin-film transistors (TFTs). In order to produce high-performance and longsustainable portable devices with the solution-processed OS TFTs, the lowoperational voltage driving current is a key issue. Experimentally, increasing the gate-insulator capacitances by high-k dielectrics in the OS TFTs has significantly improved the field-effect mobility of the OS TFTs. But, methodical examinations of how the field-effect mobility depends on gate capacitance have not been presented yet. Here, a systematic analysis of the field-effect mobility on the gate capacitances in the solution-processed OS TFTs is presented, where the multiple-trapping-and-release and hopping percolation mechanism are used to describe the electrical conductivity of the nanocrystalline and amorphous OSs, respectively. An intuitive single-piece expression showing how the field-effect mobility depends on gate capacitance is developed based on the aforementioned mechanisms. The field-effect mobility, depending on the gate capacitances, of the fabricated ZnO and ZnSnO TFTs clearly follows the theoretical prediction. In addition, the way in which the gate insulator properties (e.g., gate capacitance or dielectric constant) affect the field-effect mobility maximum in the nanocrystalline ZnO and amorphous ZnSnO TFTs are investigated.

#### 1. Introduction

Solution-processed oxide semiconductors (OSs) have received much attention due to their ability to produce transparent thinfilm transistors (TFTs) on flexible substrates cheaply, which is a

E. Lee, J. Ko, K.-H. Lim, K. Kim, S. Y. Park, Prof. Y. S. Kim Program in Nano Science and Technology Graduate School of Convergence Science and Technology Seoul National University Seoul 151-744, Republic of Korea E-mail: younskim@snu.ac.kr

Prof. J. M. Myoung Department of Materials Science and Engineering Yonsei University Seoul 120-749, Republic of Korea

Prof. Y. S. Kim

Advanced Institute of Convergence Technology 864-1 lui-dong, Yeongtong-gu Suwon-si, Gyeonggi-do 443-720, Republic of Korea

DOI: 10.1002/adfm.201400588

key in switching components for next generation displays such as smart windows, transparent mobile displays, and electronic papers.<sup>[1-9]</sup> Recently, high-quality OS films on plastic substrates have been successfully fabricated by developing lowtemperature and solution-based processes (e.g., combustion process,[3] 'sol-gel on chip' process, [4] and photochemical activation methods<sup>[5]</sup>). These methods can accelerate the adoption of flexible OS TFTs to practical applications.

While the novel OS film-fabricating techniques are important, raising drive currents in low-operating voltages is also critical for low-power consuming and high-performance OS TFTs.[10-13] One of the conventional strategies to increase the drain current ( $I_D$ ) for transistors is to increase the gate-insulator capacitances  $(C_i)$  based on the relationship of  $I_D \propto C_i$ from the metal-oxide-semiconductor fieldeffect transistors (MOSFETs) theory.[14] Empirically, such strategies has been applied to solution-processed OS TFTs.

However, the enhanced behaviors of  $I_D$  in the OS TFTs are quite different to that in MOSFETs,[3,5,10-13] since disordered metal ions or dense grain boundaries in the solution-processed OSs make the field-effect mobility ( $\mu_{EE}$ ) of the OS TFTs depend on the total number of accumulated charge carriers in the channel. [15,16] Therfore,  $\mu_{\rm FE}$  depends on  $C_{\rm i}$ , and  $I_{\rm D}$  is not in a linear relationship to  $C_i$ . The relationship between  $C_i$  and  $\mu_{FE}$ is important for low-voltage and high-performance solutionprocessed OS TFTs. Futhermore, theoretical predictions for the device performances can be essential guidelines for designing and optimizing integrated TFT circuits.

The solution-processed OS disordering states can be categorized with nanocrystalline and amorphous states, which is determined by the number of metal elements that compose the OS films. Binary oxide systems (number of metal elements = 1) such as ZnO, InO2, and SnO2, have nanocrystalline states, [6,7,12,13] while the ternary or quaternary oxide systems (number of metal elements > 1) like ZnSnO, InZnO, and InGaZnO have the amorhpous phases.<sup>[3,5,8]</sup> In the experiment, both nanocrystalline and amorhpous OS TFTs by engineering C<sub>i</sub> differ in electron-transporting mechanisms, but follow two www.afm-iournal.de

www.MaterialsViews.com

features: under high- $C_i$  conditions, maximum  $\mu_{FF}$  values of OS TFTs can be achieved with lower gate voltages than with low-C<sub>i</sub> conditions. This means that the sub-threshold swing value is reduced by increasing  $C_{i}$ . [3,5,10–13] For example, by replacing  $SiO_2$  ( $C_i = 10.8 \text{ nF cm}^{-2}$ ) with ion-gel ( $C_i = 5.08 \text{ } \mu\text{F cm}^{-2}$ ) for gate insulating materials, 14.8 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> $\mu_{FE}$  for solutionprocessed ZnO TFTs were demonstrated below the operating voltage of ≈3 V while the SiO<sub>2</sub>-gated solution-processed ZnO TFTs operated over 10 V.<sup>[13]</sup> Additionally, the maximum  $\mu_{FE}$  of the OS TFTs with high-k insulators is higher than that with low-k insulators within associated gate-bias ranges for device operations.<sup>[3,5,10,12]</sup> The photo-annealed InGaZnO TFTs on  $Al_2O_3$  gate insulator ( $C_i = 138 \text{ nF cm}^{-2}$ ) showed 9.74 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for maximum  $\mu_{FE}$  within gate-bias ranges < 10 V, while that on  $SiO_2$  ( $C_i = 17 \text{ nF cm}^{-2}$ ) showed 2.64 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for maximum  $\mu_{\rm FF}$  within gate-bias ranges < 30 V.<sup>[5]</sup> Although these demonstrations have experimentally shown the enhanced performances of the solution-processed OS TFTs, a systematic analysis about the  $C_i$  increasing  $\mu_{FE}$  for low voltage operations has not been intensively performed. In addition, the effect of gate-insulator perperties (e.g., capacitance or dielectric constant) on the maximum  $\mu_{FE}$  of the devices has not been investigated.

Here, we systematically analyze the  $C_i$ -dependent  $\mu_{FF}$  of a theoretical model representative of the solution-processed OS TFTs, where the electrical conductivity is based on the multipletrapping-and-release (MTR) mechnism for the nanocrystalline OSs or the hopping percolation mechanism for the amorhpous OSs. For both theoretical models, we derive a single-piece analytic expression, which intuitively shows how the field-effect mobility and operational gate voltages can be determined by the gate capacitance. The developed theoretical formula is successfully verified by the fabricated solution-processed ZnO or ZnSnO TFTs. At low-voltage operations of  $\approx 4$  V, the ZnO TFTs shows that its  $\mu_{FE}$  changes from 0.066 to 6.01 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> following  $\mu_{\rm FE} \propto C_{\rm i}^{1.66}$ , while the ZnSnO TFTs shows  $\mu_{\rm FE} \propto C_{\rm i}^{0.41}$ . Futhermore, we investigate how the device perperties (e.g., gate capacitances and dielectric constant of gate insulator) affect the maximum  $\mu_{FF}$ .

## 2. Development of Analytical Models for Nanocrystalline and Amorphous OS TFTs

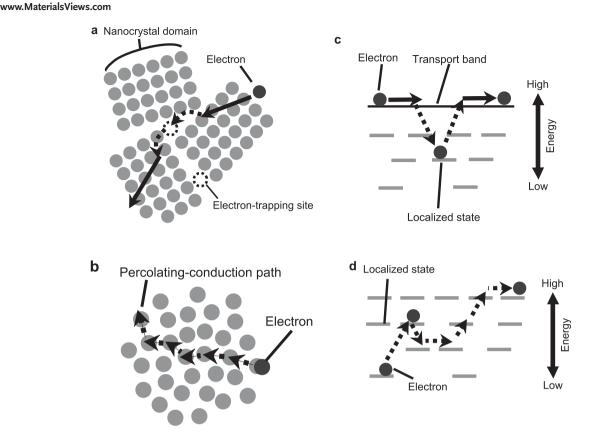

The solution-processed OSs have highly disordered states where the electrical conductivity ( $\sigma$ ) is different compared to their crystalline states ( $\sigma \propto n$ , where n is the total chargecarrier density). In the solution-processed OSs, the electron transport is limited by dense localized states between energy gaps, although the large spherical S-orbital of metal ion provides an efficient electron-transporting path.[17,18] For the nanocrystalline OSs, the electrical conduction is mainly limited to the electron-trapping sites between nanocrystal-domain boundaries (see Figure 1a).[19] The electron-trapping sites in the nanocrystalline OSs are introduced by the dense localized states between the energy gaps where the electron transport has been described by the MTR mechanism.[15,16,19] In the MTR model, most of the free electrons are assumed to be trapped in the localized states and only a small fraction of the electrons hopping to the transport bands from the localized states by thermal energy contribute temporarily to electrical conductions (see Figure 1c). Assuming the localized state distribution below the transport bands are a single exponential density of states (DOS),  $\sigma$  for the nanocrystalline OSs can be expressed as<sup>[15,16]</sup>

$$\sigma = \sigma_0 \left( \frac{\sin(\pi T/T_0)n}{(\pi T/T_0)N_t^{\text{tot}}} \right)^{\frac{I_0}{T}}$$

(1)

where  $\sigma_0$  is the conductivity prefactor,  $N_{\rm t}^{\rm tot}$  is the total number of localized states per unit volume,  $T_0$  is the characteristic temperature of the localized states representing the width of the exponential distribution below the transport bands, and T is the temperature of the device.

On the other hand, the electron transport in the amorphous OSs is governed by the thermally activated electron hopping between adjacent metal ions that hold electrons (see Figure 1b). When an external electric field is applied to the amorphous OSs, the electrons flow by the hopping process along the percolating-conduction path lying on metal ions (See Figure 1d), which determine the electrical conductivity. [18,20] We refer to this amorphous OS mechanism as the "variable-range-hopping (VRH) percolation model". In the VRH percolation model, dense localized states directly represent the disordered metal ions, and  $\sigma$  for the amorphous OSs within the localized states that follow the exponential DOS can be expressed as  $^{[20,21]}$

$$\sigma = \sigma_0 \left( \frac{\sin(\pi T/T_0)(T_0/T)^4 n}{B_c(2\alpha)^3} \right)^{\frac{T_0}{T}}$$

(2)

where  $B_{c}$ , the critical number for percolation onset, is  $\approx 2.8$  in the three-dimensional amorphous system<sup>[20]</sup> and  $\alpha$  is the effective overlap parameter for the electron-hopping process.

We assumed the following for Equation 1 and 2: 1) The single exponential DOS is given by  $g(E) = (N_t^{\text{tot}}/k_BT_0)\exp(-E/k_BT_0)$ , where E is the energy of the state and is a positive value with respect to the transport bands and the localized state density is zero above the transport bands: g(E) = 0 when E < 0.<sup>[15,20]</sup> 2) n is approximated to  $n_t$ , [15,20] and  $n_t$  is the charge-carrier density in the localized states given by [15,20]

$$n_{\rm t} = \frac{N_{\rm t}^{\rm tot} \pi T / T_0}{\sin(\pi T / T_0)} \exp\left(\frac{-q\phi_{\rm F}}{k_{\rm B} T_0}\right) \tag{3}$$

where  $\Phi_{\rm F}$  is the Fermi potential that is positive with respect to the transport bands,  $k_{\rm B}$  is the Boltzmann constant, and q is the electron charge. 3) When the device is turned on, the deep-localized states as oxygen vacancies are entirely filled up and the tail-localized states induced by disordered metal ions only influences electrical transport in the channel.<sup>[22]</sup> In both MTR and VRH percolation models, Equations 1 and 2 are valid in the range of  $T < T_0$ . [15,20]

Meanwhile,  $\mu_{FF}$  is defined as

$$\mu_{\rm FE} = \frac{L}{WC_{\rm i}V_{\rm DS}} \frac{\partial I_{\rm D}}{\partial V_{\rm GS}} \tag{4}$$

ADVANCED FUNCTIONAL MATERIALS

www.afm-journal.de

Figure 1. a,b) Schematic of electron-transporting principles for nanocrystalline (a) and amorphous (b) OSs. The orbitals of metal ions in the disordered OSs are illustrated by gray-colored circle, and oxygen ions are omitted for convenience. c,d) Schematic energy-band diagrams corresponding to the nanocrystalline (c) and the amorphous (d) OSs. In (a–d), the dash (or solid)-line arrows indicate thermally hopping (or freely moving) electron between disordered metal ions (or in nanocrystal domains).

in measured linear  $I_{\rm D}$ – $V_{\rm DS}$  output-characteristic regimes where  $I_{\rm D}$  is the electrical current passing through the drain electrode,  $V_{\rm GS}$  (or  $V_{\rm DS}$ ) is the applied voltage between the gate (or drain) and the source electrode, and W and L are the width and length of the channel in the semiconductor film, respectively. In thin-film transistors,  $I_{\rm D}$  can be determined by

$$I_{\rm D} = \frac{W}{L} \int_0^{V_{\rm DS}} \int_{\varphi_{\rm s}}^{V_{\rm ch}} \frac{\sigma}{(\nabla \varphi)_{\rm tr}} \exp\left(\frac{q(\varphi - V_{\rm ch})}{k_{\rm B}T}\right) d\varphi dV_{\rm ch}$$

(5)

where  $\varphi$  is the electrostatic potential in the channel and subscript u depicts the normal direction vector component to the channel-gate insulator interface. The exponential term in the integral represents quasi-Fermi potentials in the OS film at non-equilibrium condition.  $\varphi_s$  is the electrostatic potential at the channel and gate insulator interface, which satisfies the boundary conditions given by  $V_{GS} = V_{FB} + \varepsilon_0 \varepsilon_s |(\nabla \varphi_s)_u|/C_i + \varphi_s$ . In this case,  $V_{FB}$  is the flat-band voltage,  $\varepsilon_0$  is the electrical permittivity in a vacuum, and  $\varepsilon_s$  is the relative permittivity of the OSs. We refer to  $\varphi_s$  as the surface potential of the channel. At the OS bulk, which is far from the channel-gate insulator interface, the electrostatic potential is  $\varphi = V_{ch}$ .  $V_{ch} = V_{DS}$  is assumed to be at the drain electrode while  $V_{ch} = 0$  is at the source electrode. [16]

After substituting Equation 1 (for the MTR model) or 2 (for the VRH percolation model) into Equation 5, taking the integral

with mathematical manipulations using gradual channel approximation  $^{[14,16,23]}$  leads to an explicit expression of  $I_D$ :

$$I_{D} = \sigma_{0} \delta \frac{W}{L} \frac{V_{T}}{\gamma - 1} \left( \sqrt{\frac{2\varepsilon_{0} \varepsilon_{s} k_{B} T_{0} \sin(\pi T / T_{0})}{q^{2} N_{t}^{tot} \pi T / T_{0}}} \right)^{\gamma} \left( \frac{C_{i}}{\varepsilon_{0} \varepsilon_{s}} \right)^{\gamma - 1}$$

$$\times \left\{ \left[ \frac{V_{GS} - V_{FB} - \varphi_{sS}}{\gamma V_{T}} + \frac{\gamma}{\gamma - 1} \right] \left[ \frac{V_{GS} - V_{FB} - \varphi_{sS}}{\gamma V_{T}} \right]^{\gamma - 1} \right\}$$

$$- \left[ \frac{V_{GS} - V_{FB} - \varphi_{sD}}{\gamma V_{T}} + \frac{\gamma}{\gamma - 1} \right] \left[ \frac{V_{GS} - V_{FB} - \varphi_{sD}}{\gamma V_{T}} \right]^{\gamma - 1} \right\}$$

$$(6)$$

where  $V_{\rm T}=k_{\rm B}T/q$  is the thermal voltage and  $\gamma=2T_0/T$ . In Equation 6,  $I_{\rm D}$  for the MTR model (or VRH percolation model) is calculated by taking  $\delta=1$  (or  $\delta=[\pi(T_0/T)^3N_{\rm t}^{\rm tot}/B_{\rm c}(2\alpha)^3]^{(T_0/T)}$ ).  $\phi_{\rm sS}$  and  $\phi_{\rm sD}$  are the surface potential at the source and drain electrodes, respectively. These are expressed as

$$\frac{\varphi_{\text{sS}} = V_{\text{GS}} - V_{\text{FB}} - \gamma V_{\text{T}} W_{0}}{\sqrt{\frac{q^{2} N_{\text{t}}^{\text{tot}} \pi T / T_{0}}{2\varepsilon_{0} \varepsilon_{s} k_{\text{B}} T_{0} \sin(\pi T / T_{0})}} \frac{\varepsilon_{0} \varepsilon_{\text{s}}}{C_{\text{i}}} \exp\left(\frac{V_{\text{GS}} - V_{\text{FB}} - \phi_{\text{F}}}{\gamma V_{\text{T}}}\right) \right]$$

(7-1)

and

$$\varphi_{\text{sD}} = V_{\text{GS}} - V_{\text{FB}} - \gamma V_{\text{T}} W_{0}$$

$$\left[ \sqrt{\frac{q^{2} N_{\text{t}}^{\text{tot}} \pi T / T_{0}}{2\varepsilon_{0} \varepsilon_{s} k_{\text{B}} T_{0} \sin(\pi T / T_{0})}} \frac{\varepsilon_{0} \varepsilon_{\text{s}}}{C_{\text{i}}} \exp\left(\frac{V_{\text{GS}} - V_{\text{FB}} - \phi_{\text{F}} - V_{\text{DS}}}{\gamma V_{\text{T}}}\right) \right]$$

(7-2)

where W<sub>0</sub> represents the principal branch of the Lambert Function.

Calculating  $\mu_{FE}$  with Equation 6 and 7 yields

$$\mu_{\text{FE}} = \frac{\beta}{C_{\text{i}}} \left\{ \left[ \frac{q n_{\text{s}}}{\gamma V_{\text{T}}} \right]^{\gamma - 1} - \left[ \frac{q n_{\text{d}}}{\gamma V_{\text{T}}} \right]^{\gamma - 1} \right\}$$

(8)

where  $n_{\rm s}$  (or  $n_{\rm d}$ ) =  $\varepsilon_0 \varepsilon_{\rm s} |(\nabla \phi_{\rm sS})_{\rm u}|$  (or  $\varepsilon_0 \varepsilon_{\rm s} |(\nabla \phi_{\rm sD})_{\rm u}|$ ) is the accumulated charge carrier density at the source (or drain) electrodes and  $\beta = \frac{\sigma_0 \delta}{V_D(\gamma^{-1})} \left( \sqrt{\frac{2\varepsilon_0 \varepsilon_k k_0 T_0 \sin(\pi T/T_0)}{q^2 N_0^{16} \pi T/T_0}} \right)^{\gamma} \left( \frac{1}{\varepsilon_0 \varepsilon_s} \right)^{\gamma-1}$ . Equation 8 reveals that raising the total number of charge carrier is important for high  $\mu_{\text{FE}}$ , when the trap DOS in the OSs follows the exponential distributions. For the  $V_{\rm GS}-V_{\rm FB} \geq V_{\rm DS}$  region, the surface potentials can be approximated to  $\varphi_{\rm sS}\approx 0$  and  $\varphi_{\rm sD}\approx V_{\rm DS}.^{[16,23]}$ In this case,  $n_s$  (or  $n_d$ ) is written as  $n_s$  (or  $n_d$ )  $\approx C_i(V_{GS} - V_{FB})/q$ (or  $C_{\rm i}(V_{\rm GS}-V_{\rm FB}-V_{\rm DS})/q$ ) and Equation 8 is then expressed as

$$\mu_{\text{FE}} \cong \beta \left\{ \left[ \frac{V_{\text{GS}} - V_{\text{FB}}}{\gamma V_{\text{T}}} \right]^{\gamma - 1} - \left[ \frac{V_{\text{GS}} - V_{\text{FB}} - V_{\text{DS}}}{\gamma V_{\text{T}}} \right]^{\gamma - 1} \right\} C_{\text{i}}^{\gamma - 2}$$

(9)

which clearly shows how  $\mu_{FE}$  can be determined by  $V_{GS}$  and  $C_i$ . To reach the equal- $\mu_{FE}$  value, high- $C_i$  conditions require smaller  $V_{GS}$  than in low- $C_i$  conditions. The validity of assumption in Equation 9 is discussed later in the paper. In addition, when we examine the  $C_i$ -dependent  $\mu_{FE}$  with holding other device parameters, Equation 9 is reduced simply to

$$\mu_{\rm FE} \cong \mu_{\rm FE}^0 \left(\frac{C_{\rm i}}{C_{\rm i}^0}\right)^{\gamma-2} \tag{10}$$

where  $\mu^{0}_{FE}$  is the field-effect mobility at  $C_{i} = C_{i}^{0}$ . Equation 10 clearly shows that the  $\mu_{FE}$  of nanocrystalline (or amorphous) TFTs strongly depend on the  $C_i$  variation. Increasing  $C_i$  results in increasing  $\mu_{FE}$  in the same  $V_{GS}$  values.

### 3. Field-Effect Mobility Analysis Depending on Gate Capacitance using Model Devices

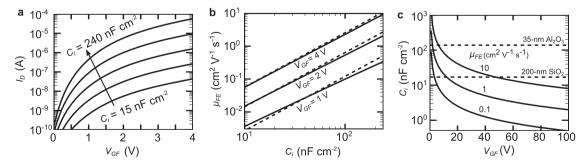

We first investigate how  $C_i$  affect the transfer characteristics of the MTR (or VRH percolation) model-based TFTs when the devices turn on (meaning the regime of  $V_{GS} \ge V_{FB}$ ). According to Equation 6, the device characteristics of both TFT models are analogous to each other, so the MTR model is used to study the essential device physics. Figure 2a shows calculated  $I_D$ - $V_{GF}$  $(V_{GF} = V_{GS} - V_{FB})$  transfer curves using Equation 6 for the device with various  $C_i$  (15 nF cm<sup>-2</sup> to 240 nF cm<sup>-2</sup>). Other device parameters are listed in Table 1. The calculated  $I_{\rm D}$ - $V_{\rm GF}$  curves are representative of the solution-processed OS TFT transfer characteristics. The drain current transitions from a low V<sub>GF</sub> to a high  $V_{GF}$  smoothly in log-scale. [3-13,16,24] By increasing  $C_i$ ,  $I_D$ as a function of  $V_{GF}$  grows more rapidly within the  $V_{GF}$  region of 0 V <  $V_{GF}$  < 4 V. The sub-threshhold swing value, defined by  $dV_{GF}/d(\log I_{\rm D})$ , significantly decreases when just increasing  $C_{\rm i}$ . Unlike conventional MOSFETs theory, the simulation results (or Equation 6) show that  $I_D$  of OS TFTs with the exponential trap DOS are in a nonlinear relationship with  $C_i$  (i.e., depends on  $\approx C_i^{\gamma-1}$ ).

Figure 2b shows the calculated  $\mu_{FE}$  as a function of  $C_i$  using Equation 8 at  $V_{GF} = 1$ , 2, and 4 V. All other device parameters are fixed as given in Table 1.  $\mu_{FE}$  increases with increasing  $V_{GF}$ , which also describes well-known characteristics of the gatebias-dependent  $\mu_{\text{FE}}$  for the solution-processed OS TFTs. [4,11,24]  $\mu_{\rm FE}$  notably increases with increasing  $C_{\rm i}$  within the  $C_{\rm i}$  region of 10 nF cm<sup>-2</sup> <  $C_i$  < 240 nF cm<sup>-2</sup>. These calculated  $\mu_{FE}$ – $C_i$ characteristics closely follow the dotted lines plotted using Equation 9, indicating that  $\mu_{FE}$  follows a power-law dependent on  $C_i^{\gamma-2}$  shown in Equation 10. Since the surface potentials monotonically increases with increasing  $C_i$ , the  $\mu_{FE}$ - $C_i$  calculated curves slightly deviate from the dotted lines for the higher  $C_i$ . These small deviations are more obvious when  $V_{GF}$ approaches  $V_{\rm DS}$ . However, the surface potential variations when  $C_i$  varies are not dominant enough to determine  $\mu_{FE}$ . Therefore, the assumption in Equation 9 is still valid.

Using Equation 9, we also examine the relationship between  $C_{\rm i}$  and  $V_{\rm GF}$  when the  $\mu_{\rm FE}$  value is maintained. Figure 2c shows the  $C_i$ - $V_{GF}$  characteristics under  $\mu_{FF} = 0.1$ , 1, and 10 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. As expected, the  $\mu_{FE}$  value under high- $C_i$  conditions is easily

Figure 2. Calculated device performances on variation of the gate-insulator capacitance (C<sub>i</sub>) for the MTR-model based TFTs. a) The calculated drain current  $(I_D) - V_{GF} [V_{GF} = \text{the gate-source voltage } (V_{GS})$ —the flat-band voltage  $(V_{FB})$ ] transfer characteristics with varying  $C_i$  from 15 to 240 nF cm<sup>-2</sup> (from bottom to top: 15, 30, 60, 120, 240 nF cm<sup>-2</sup>), using Equation 6 with the parameters in Table 1. b) The calculated field-effect mobility ( $\mu_{FF}$ ) as a function of  $C_i$  using Equation 8 (solid lines) and Equation 9 (dash lines) for the case of a at  $V_{GF} = 1$ , 2, and 4 V. c) Calculated  $C_{i}$ — $\mu_{FE}$  characteristics under  $\mu_{FE} = 1$ 0.1, 1,  $10 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ . The dash lines indicate the  $C_i$  values of 35-nm-thick  $\text{Al}_2\text{O}_3$  (top) and 200-nm-thick  $\text{SiO}_2$  (bottom) insulator.

ADVANCED FUNCTIONAL MATERIALS

www.afm-journal.de

**Table 1.** Device parameter values for the model devices in Figure 2.

| Variables          | Values                 | Units<br>µm     |  |

|--------------------|------------------------|-----------------|--|

| W                  | 1000                   |                 |  |

| L                  | 50                     | μm              |  |

| $V_D$              | 1                      | V               |  |

| $V_{S}$            | 0                      | V               |  |

| $arepsilon_{ m s}$ | 7.5                    | -               |  |

| T                  | 293                    | K               |  |

| $T_0$              | 535.5                  | K               |  |

| $N_{t}^{tot}$      | $8.55 \times 10^{-19}$ | $cm^{-3}$       |  |

| $\sigma_0$         | 7.02                   | $\rm S~cm^{-1}$ |  |

| $arPhi_{F}$        | 0.2                    | eV              |  |

achieved with low- $V_{GF}$  values. We assume that there are two types of solution-processed OS TFTs, for comparing the calculated C<sub>i</sub>-V<sub>GF</sub> characteristics with reported experimental results:<sup>[5]</sup> one with a 200 nm-thick  $SiO_2$  ( $C_i = 17 \text{ nF cm}^{-2}$ ) layer for the gate insulator and the other with a 35 nm-thick  $Al_2O_3$  ( $C_i = 138 \text{ nF cm}^{-2}$ ). To achieve  $\mu_{FE} = 0.1 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , 4 V is sufficient as the maximum  $V_{\rm GF}$  for both devices. When  $\mu_{\rm FE}=1~{\rm cm^2~V^{-1}~s^{-1}}$ , the SiO<sub>2</sub> device requires 12 V for the  $V_{\rm GF}$  while the  ${\rm Al_2O_3}$  device only needs 2 V. For higher  $\mu_{FE}$  (>1 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>), the required voltage values for the SiO<sub>2</sub> device are more increase than that for the Al<sub>2</sub>O<sub>3</sub> device; When  $\mu_{FE}$  is 10 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, the SiO<sub>2</sub> device requires  $V_{GF} = 47$  V while the  $Al_2O_3$  device requires only  $V_{GF} = 6$  V. Meanwhile, these results suggest that ideal gate insulators, which is an perfect electrical insulating material (the dielectric-breakdown voltage is infinite, and the gate-leakage current at infinite  $V_{\rm GF}$  is zero), can achieve any desired- $\mu_{FE}$  value with the required gate bias regardless of the Ci values. However, realistic gate insulator have nonzero gate-leakage currents and finite dielectric-breakdown voltages. In addition, the  $\mu_{FE}$  increment is scattering-limited, which will be discussed in the experimental results. Therefore, a consideration for such aspect is necessary, although a simple examination of Equation 9 describes the possible low-voltage operation of the OS TFTs under high-*C*<sub>i</sub> conditions.

## 4. Structure and Material Properties of Solution-Processed ZnO and ZnSnO TFTs

To verify this theoretical approach, we fabricated solution-processed OS TFTs based on a conventional bottom-gate

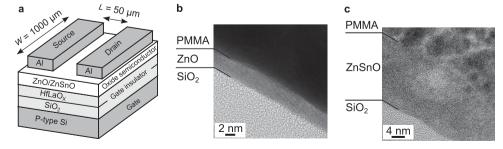

top-contact structure with L of 1000 µm and W of 50 µm, as shown in Figure 3a. For the OS channel layer, solution-processed nanocrystalline ZnO (see Figure 3b) or amorphous ZnSnO (see Figure 3c) films were applied. The dielectric SiO<sub>2</sub> and amorphous HfLaOx layer thicknesses as gate insulators were tuned in order to change C<sub>i</sub>. The capacitors of p-type Si/SiO<sub>2</sub>/HfLaO<sub>x</sub>/Al were fabricated to characterize C<sub>i</sub> and the SiO<sub>2</sub> and HfLaO<sub>x</sub> thickness in each capacitor is equal to that of the corresponding OS TFTs. The capacitors were designed in squares of 300  $\mu m \times 300 \mu m$ , the capacitances of which measured under AC bias with a frequency of 20 Hz vary from 13 nF cm<sup>-2</sup> to 203 nF cm<sup>-2</sup>. Due to a high dielectric constant and good insulating property of the amorphous HfLaO<sub>x</sub> layer, [25,26] the capacitors maintains a low dissipation factor of ~3% at 20 Hz. In all ZnO (or ZnSnO) TFTs, the HfLaO<sub>x</sub> layer ensured an equal interface between the gate insulator and ZnO (or ZnSnO) films. Other device fabrication details are provided in the Experimental Section.

# 5. Verification of a Single-Piece Formula for Gate Capacitance-Dependent Field-Effect Mobility using Solution-Processed ZnO and ZnSnO TFTs

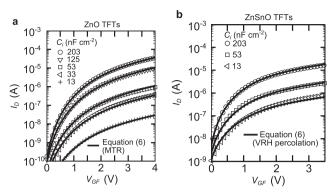

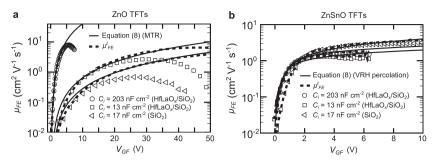

To validate Equation 6, we measured both  $I_D$ - $V_{DS}$  output and  $I_{\rm D}$ - $V_{\rm GS}$  transfer characteristics of the ZnO TFTs (and ZnSnO TFTs) with  $C_i = 203$  nF cm<sup>-2</sup>. The measured experimental curves clearly fit Equation 6 (see Figure S1 in Supporting information), which validates that the developed theoretical model well describes the electron-transporting mechanisms of ZnO and ZnSnO TFTs. To plot the transfer characteristics for the devices on the  $I_{\rm D}\!\!-\!V_{\rm GF}$  axes,  $V_{\rm FB}$  was determined by fitting the measured  $I_{\rm D}\!\!-\!V_{\rm GS}$  curves using Equation 6, with the device parameters depicted in Table 2. The  $I_D$ - $V_{GS}$  curves for the ZnO TFTs (or ZnSnO TFTs) were fitted using the MTR (or VRH percolation) model. Figure 4a,b show the  $I_D$ - $V_{GF}$  transfer characteristics for the ZnO and ZnSnO TFTs (symbols) at various  $C_i$  under  $V_{DS} = 1$  V, respectively. The measured  $I_D$ – $V_{GF}$ curves increase more rapidly for the device with the higher C<sub>i</sub> within the region of 0 V <  $V_{GF}$  < 4 V for all solution-processed OS TFTs. This agrees with the theoretical predictions given in Figure 2a. Moreover, the measured  $I_D$ – $V_{GF}$  curves obviously fit Equation 6 (solid lines in Figure 4a,b).  $T_0$ ,  $N_t^{\text{tot}}$ , and  $\sigma_0$  for the MTR model and  $T_0$ ,  $N_t^{\text{tot}}$ ,  $\sigma_0$ ,  $\alpha$  for the VRH percolation model, respectively, represent the essential physical properties of the

Figure 3. Structure and material properties of solution-processed OSs TFTs. a) Schematic structure of solution-processed ZnO (or ZnSnO) TFTs. b,c) Cross-sectional transmission electron microscope images of  $Si/SiO_2/ZnO$  (a) (or ZnSnO (b))/poly (methyl methacrylate) (PMMA) specimens.

www.afm-journal.de

www.MaterialsViews.com

ZnO and ZnSnO layers. Therefore, the results in Figure 4a (or 4b) suggest that i) the electronic structures of the ZnO (or ZnSnO) layer in all ZnO (or ZnSnO) devices are nearly identical and ii) the differences in the measured  $I_{\rm D}$  between the ZnO (or ZnSnO) TFTs under the different- $C_{\rm i}$  conditions in Figure 4a (or 4b) arise entirely from the variation of  $C_{\rm i}$  between the devices.

The fitted  $V_{\rm FB}$  for the ZnO (or ZnSnO) TFTs varies from  $-0.96\,\rm V$  to  $1.80\,\rm V$  (or from  $0.12\,\rm V$  to  $0.29\,\rm V$ ). To prevent shifting  $V_{\rm FB}$  by moisture adsorption and photo doping of the OS film,  $^{[27,28]}$  the transfer characteristics were measured in a vacuum ( $\sim 10^{-3}\,\rm Torr$ ) and in the dark, respectively. The work-function differences between the gate electrode and the ZnO (or ZnSnO) layer may be non-responsible to the variation of the fitted  $V_{\rm FB}$ , since the physical properties of the ZnO (or ZnSnO) layer were almost equal and the gate electrode was a p-type Si for all devices. Therefore, the small differences in the fitted  $V_{\rm FB}$  can be attributed to unintended oxide charges in the gate insulator. [14]

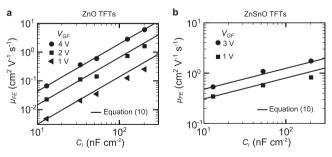

$\mu_{\rm FE}$  for the ZnO (or ZnSnO) TFTs were calculated with  $\gamma$ = 3.66 (or  $\gamma$ = 2.41) at various  $V_{\rm GF}$  in Equation 10 as shown in solid lines in **Figure 5**a (or 5b) (the measured  $\mu_{\rm FE}$  from the ZnO (or ZnSnO) TFTs with the lowest  $C_{\rm i}$  was used as  $\mu^0_{\rm FE}$  and  $C_{\rm i}^{\rm o}$ ). Figure 5 also shows the measured  $\mu_{\rm FE}$  for the ZnO and ZnSnO TFTs (symbols). In both cases, the measured  $\mu_{\rm FE}$ – $C_{\rm i}$  characteristics follow the solid lines calculated by Equation 11. This indicates that the  $\mu_{\rm FE}$  of the solution-processed OS TFTs follow a power-law dependence on  $C_{\rm i}^{\gamma-2}$ , as discussed in this theoretical study. Thus,  $\mu_{\rm FE} \propto C_{\rm i}^{1.66}$  for the ZnO TFTs and  $\propto C_{\rm i}^{0.41}$  for the ZnSnO TFTs. At low operating regions (1 V  $\leq$  V $_{\rm GF} \leq$  4 V),  $\mu_{\rm FE}$  of both the ZnO and ZnSnO devices increases with increasing  $C_{\rm i}$  (within the region of 13 nF cm $^{-2}$  <  $C_{\rm i}$  < 203 nF cm $^{-2}$ ). For the ZnO TFTs, notably,  $\mu_{\rm FE}$  is 0.066 cm $^2$  V $^{-1}$  s $^{-1}$  at  $C_{\rm i}$  = 13 nF cm $^{-2}$  and increases to 6.01 cm $^2$  V $^{-1}$  s $^{-1}$  at  $C_{\rm i}$  = 203 nF cm $^{-2}$  when  $V_{\rm GF}$  is 4 V.

The increases in  $\mu_{FE}$  can be explained by lowering the activation energy ( $E_a$ ) of  $\mu_{FE}$ . The most conventional method to derive  $E_a$  is to examine the T-dependent  $\mu_{FE}$  using the Arrhenius equation ( $\propto \exp(-E_a/k_BT)$ ). [15,16,19,20] By correlating Equation 10 to the Arrhenius equation,  $E_a$  for  $\mu_{FE}$  can be expressed in terms of  $C_i$  as

$$E_{\rm a} = E_{\rm a}^0 - 2k_{\rm B}T_0 \ln \left(\frac{C_{\rm i}}{C_{\rm i}^0}\right) \tag{11}$$

where  $E_a{}^0$  is the activation energy at  $C_i = C_i{}^0$ . Equation 11 reveals that  $E_a$  monotonically decreases when  $C_i$  is increased. In both the MTR and VRH percolation models, the increment of  $C_i{}^0$  makes electrons rapidly fill the lower-lying localized states of the solution-processed OSs, which allows the additionally accumulating electrons to occupy the upper-lying localized states. Consequently, the electrons easily jump to the transport bands (for the MTR model) or neighboring localized states in the percolating path (for the VRH percolation model), which result in decreasing  $E_a$  and increasing  $\mu_{\rm FE}$ .

Although the fundamental electron-transporting mechanisms of both the amorphous and nanocrystalline OSs are different from each other, Equation 10 indicates that the  $\mu_{\text{FF}}$ of both models depends on the  $C_i$  variation. Furthermore, Equation 10 explains that this dependency becomes stronger in the OSs with a higher  $T_0$ . In our results,  $\mu_{FF}$  for the ZnO TFTs depend more on the variation of C<sub>i</sub> than that for the ZnSnO TFTs, since  $T_0$  for the ZnO TFTs is higher than that for the ZnSnO TFTs. These results correspond with previously reported studies which describe that the large 5S-orbitals of Sn-ions allow electron clouds to well overlap between adjacent metal ions in the ZnSnO amorphous system, and then the localized states have low electron-trapping energy. [29] In addition, the ZnSnO film was thermally annealed at 500 °C, which is higher than the annealing temperature for the ZnO film (300°C). Since high-temperature annealing makes the OSs film have denser packing structures,[18] it decreases the neighbor-toneighbor distance between metal ions, which may decrease  $T_0$ . At a limit that satisfies  $T \approx T_0$ ,  $\mu_{FE}$  will not depend on  $C_i$ . This means that the limitations by the localized states in the electron transport are completely overcome by the thermal energy. Since our models are valid for  $T < T_0$ , Equation 10 cannot be applied to TFTs based on crystalline OSs ( $T_0 \approx 0$ ) or TFTs under hightemperature operation  $(T > T_0)$ .

For saturation mobility ( $\mu_{\rm Sat}$ ) where the mobility is measured at saturated  $I_{\rm D}$ – $V_{\rm DS}$  output regimes, an expression as a function of  $V_{\rm GF}$  and  $C_{\rm i}$  can be calculated from Equation 6 (see Equation S1 in Supporting information). The dependence of  $\mu_{\rm Sat}$  on  $C_{\rm i}$  is equal to that for  $\mu_{\rm FE}$  since  $\mu_{\rm Sat} \sim C_{\rm i}^{\gamma-2}$  according to Equation S1. An experimental investigation on  $\mu_{\rm Sat}$  will be conducted in future works, since this study only focuses on the field-effect mobility.

**Table 2**. Parameters for fitting Equation 6 to transfer characteristics of solution-processed OSs TFTs, and calculated conductivities of solution-processed OS layers.

| Variables          | MTR (for ZnO TFTs)                   |                         | VRH percolation (for ZnSnO TFTs)     |                         | Units              |

|--------------------|--------------------------------------|-------------------------|--------------------------------------|-------------------------|--------------------|

| Insulator          | HfLaO <sub>x</sub> /SiO <sub>2</sub> | 200-nm SiO <sub>2</sub> | HfLaO <sub>x</sub> /SiO <sub>2</sub> | 200-nm SiO <sub>2</sub> | _                  |

| $\Gamma_0$         | 535.5 ± 0.4                          | 538.1                   | 353.5 ± 0.5                          | 381.3                   | К                  |

| $V_t^{\text{tot}}$ | $8.55 \pm 0.04 \times 10^{18}$       | $8.36 \times 10^{18}$   | $1.95 \times 10^{19}$                | $1.95 \times 10^{19}$   | cm <sup>-3</sup>   |

| $\sigma_0$         | $7.02 \pm 0.03$                      | 2.79                    | $1.10 \pm 0.08 \times 10^{8}$        | $5.75\times10^8$        | S cm <sup>-1</sup> |

| ı                  | -                                    |                         | $9.42 \pm 0.41 \times 10^{7}$        | $9.56\times10^7$        | $cm^{-1}$          |

| $\sigma^{a)}$      | $2.5 \times 10^{-3}$                 | $1.0 \times 10^{-3}$    | $1.9 \times 10^{-2}$                 | $4.0 \times 10^{-2}$    | $\rm S~cm^{-1}$    |

$<sup>^{</sup>m a)}\sigma$  for ZnO and ZnSnO layers in the devices were calculated using Equations 1 and 2, respectively.

ADVANCED FUNCTIONAL MATERIALS

www.afm-journal.de www.MaterialsViews.com

**Figure 4.** Transfer characteristics of the solution-processed OSs TFTs with various gate-insulator capacitances  $(C_i)$ . a,b) The measured drain currents  $(I_D)-V_{GF}$   $[V_{GF}=$  the gate-source voltage  $(V_{GS})-$  the flat-band voltage  $(V_{FB})]$  transfer characteristics (symbols) of the ZnO (a) and ZnSnO (b) TFTs with various  $C_i$  from 13 nF cm<sup>-2</sup> to 203 nF cm<sup>-2</sup>, under a drain-source voltage  $(V_{DS})$  of 1 V. Solid lines indicate theoretical fits to Equation 6. The MTR (or VRH percolation) model is used for the ZnO (or ZnSnO) TFTs.

#### 6. Investigation of the Maximum Field-Effect Mobility of the ZnO and ZnSnO TFTs in Various Gate Insulator Properties

We next examine the maximum  $\mu_{FE}$  of the devices under different- $C_i$  conditions. The ZnO (or ZnSnO) TFTs with  $C_i$  = 13 and 203 nF cm<sup>-2</sup> were selected, and the  $V_{GS}$  values for the devices were swept until the measured  $I_D$  were saturated (under  $V_{DS} = 1$  V). Figure 6 shows the measured  $\mu_{FE}$  as a function of  $V_{GF}$ . The measured  $\mu_{FE}$  for the ZnO TFT with  $C_i$  = 203 nF cm<sup>-2</sup> (circle symbols in Figure 6a) rapidly increases and follows theoretical predictions (solid line) within  $V_{GF} < 3.8$  V. It deviates the theoretical prediction for the region of  $V_{GF} > 3.8$  V. The measured  $\mu_{FE}$  has a maximum value of 7.93 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at  $V_{GF} = 5.7$  V, which decreases for  $V_{GF} > 5.7$  V. These mobility degradations are likely due to enhanced electron-to-electron or surface-roughness scattering effects at the HfLaO<sub>x</sub> and ZnO interfaces, since increased gate-electric fields make the channel electrons move toward the insulator/semiconductor interfaces. [30,31]

Meanwhile, the maximum  $\mu_{FE}$  of the ZnO TFTs at  $C_i = 13 \text{ nF cm}^{-2}$  (square symbols in Figure 6a) is smaller than that of

**Figure 5.** The measured field-effect mobility ( $\mu_{FE}$ ) depending on the gate-insulator capacitance ( $C_i$ ) of the solution-processed OSs TFTs. a,b) The measured  $\mu_{FE}-C_i$  characteristics (symbols) of the ZnO (a) and ZnSnO (b) TFTs under various  $V_{GF}$  [ $V_{GF}$  = the gate-source voltage ( $V_{CS}$ ) – the flat-band voltage ( $V_{FB}$ )]. Solid lines indicate theoretical results calculated using Equation 10. In (a,b), the drain-source voltage ( $V_{DS}$ ) is 1 V.

the device with  $C_i = 203 \text{ nF cm}^{-2}$ . In this case, the diminished  $\mu_{\rm FE}$  mainly arises from leakage currents,  $I_{\rm leak}$ , flowing from gate to drain electrode (the current direction of  $I_{leak}$  is reverse to that of  $I_D$ ). To examine the  $I_{leak}$  effect on the mobility, the measured  $\mu_{\rm FE}$  for total current,  $I_{\rm tot} = |I_{\rm D}| + |I_{\rm leak}|$ , are also plotted and the field-effect mobility for the total current is referred to as  $\mu_{\text{FE}}^{\text{t}}$ . As shown in Figure 6a, the differences between  $\mu_{FE}^{t}$  (dash line) and  $\mu_{\rm FE}$  at  $C_{\rm i}=13~{\rm nF~cm^{-2}}$  are obvious, while  $\mu_{\rm FE}^{\rm t}$  and  $\mu_{\rm FE}$  at  $C_i = 203 \text{ nF cm}^{-2}$  are nearly equal. At  $V_{GF} = 47.7 \text{ V}$ , the  $\mu^t_{FE}$ at  $C_i = 13 \text{ nF cm}^{-2}$  has the maximum value, which is comparable to the maximum  $\mu_{FE}$  at  $C_i = 203$  nF cm<sup>-2</sup>. For the region where  $V_{GF} > 47.7$  V, the  $\mu_{FE}^{t}$  at  $C_i = 13$  nF cm<sup>-2</sup> also decreases due to the increased scattering effects. The detrimental effect of  $I_{leak}$  on the  $\mu_{FE}$  becomes larger for the ZnO TFT with a single 200-nm-thick  $SiO_2$  insulator ( $C_i = 17 \text{ nF cm}^{-2}$ ). In Figure 6a, the maximum  $\mu_{FF}$  is 0.684 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> as shown as triangles, while the maximum  $\mu_{FE}^{t}$  is 4.19 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>.

The measured  $I_{leak}$  comes from the gate insulator/the OSs junctions, since the currents for P-Si/gate insulator/Al structures are less than 10<sup>-9</sup> A in the estimated voltage regions. The  $I_{leak}$  –  $V_{GS}$  characteristics are similar to that for diodes as I<sub>leak</sub> turns on and increases only with positive bias for the gate electrode and negative bias for the semiconductors. Ileak may be related to the trap-assisted hopping in thermally grown SiO<sub>2</sub> and solution-processed HfLaOx (where the energy levels of the traps in the insulator are comparable to the mobile bands of the OSs), since the leakage current of the ZnO TFTs is very low with high quality SiO2 that was grown by plasma-enhanced chemical vapor deposition methods.<sup>[31]</sup> We also found that the turn-on voltage of the  $I_{\text{leak}}$  depends on the gate insulator thickness, and that the dependence of  $I_{\text{leak}}$  on  $C_{\text{i}}$  is different to  $I_{\text{D}}$ , although detail mechanisms have not been investigated. In the case of the ZnO TFTs with  $C_i = 203 \text{ nF cm}^{-2}$ ,  $I_{leak}$  insignificantly affect until  $\mu_{FE}$  reaches its scattering-limited maximum. However,  $I_{leak}$  for the ZnOs TFTs with  $C_i = 13 \text{ nF cm}^{-2}$  is comparable to  $I_D$  at  $V_{GF}$  of  $\approx 15$  V, where  $\mu_{FE}$  is only 1.3 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. In the case of the ZnO TFTs with the single 200-nm-thick SiO<sub>2</sub> insulator,  $I_{\text{leak}}$  is more quickly comparable to  $I_{\text{D}}$  than the device with  $C_{\rm i}$  = 13 nF cm<sup>-2</sup>, which severely disturbs  $\mu_{\rm FE}$  enough to make it increase.

However, the  $\mu_{\rm FE}$  –  $V_{\rm GF}$  characteristics of the ZnSnO TFTs with 13 and 203 nF cm<sup>-2</sup> are very similar to each other, as shown in Figure 6b. Since the energy depth of the localized states that correspond to  $T_0$ , is very small for the ZnSnO TFTs, the dependency of  $\mu_{\rm FE}$  on  $C_{\rm i}$  is weak according to Equation 9. For the region of 0 V <  $V_{\rm GF}$  < 6 V, the measured  $\mu_{\rm FE}$  for both devices have maximum values, and decrease according to the electron-scattering effect. Because  $I_{\rm leak}$  is not dominant in the  $V_{\rm GF}$  region, the measured  $\mu_{\rm FE}$  and  $\mu^{\rm t}_{\rm FE}$  are almost identical for both devices. Such characteristics are also observed in the ZnSnO TFTs with single 200-nm-thick SiO<sub>2</sub> insulators, as shown in triangle symbols in Figure 6b; the trap-characteristic temperature is ~373 K and the differences between  $\mu_{\rm FE}$  and  $\mu^{\rm t}_{\rm FE}$  can be ignored when 0 V <  $V_{\rm GF}$  < 10 V.

The absence of  $I_{\rm leak}$  effects (possible by reducing the source/drain electrode size or by replacing thermally grown  ${\rm SiO_2}$  with other high quality insulators)[31] show that the gate-insulator capacitance cannot be main factor that determines the maximum  $\mu_{\rm FE}$  of the solution-processed OS TFTs, but rather that

www.afm-iournal.de

www.MaterialsViews.com

**Figure 6.** a,b) The measured field-effect mobility ( $\mu_{FE}$ ) as a function of  $V_{CF}$  [ $V_{CF}$  = the gate-source voltage ( $V_{CS}$ ) – the flat-band voltage ( $V_{FB}$ )] for the ZnO (a) and ZnSnO (b) TFTs. Solid lines indicate theoretical results using Equation 8; the MTR (or VRH percolation) model is used for the ZnO (or ZnSnO) TFTs. Dash lines indicate the field-effect mobility for the total current. In (a,b), the drain-source voltage ( $V_{DS}$ ) is 1 V.

the physical properties of the gate insulator/OS interfaces are critical. The measured  $\mu^{t}_{FE}$  of the ZnO TFTs perform better in HfLaOx/ZnO interfaces than SiO2/ZnO interfaces, while the ZnSnO TFTs show higher  $\mu_{FE}^{t}$  values in SiO<sub>2</sub>/ZnSnO interfaces than in HfLaO<sub>x</sub>/ZnSnO interfaces. Additionally, we calculated the electrical conductivity of the ZnO (or ZnSnO) films in the devices by using Equation 1 (or 2) with the fitting parameters in Table 2. The calculated conductivity orders of magnitude are similar to the bulk conductivity of the solution-processed ZnO and ZnSnO films.<sup>[8,32]</sup> Meanwhile, the conductivities are affected by physical properties of the gate insulator/ZnO (or ZnSnO) interfaces in the devices. As a result, the ZnO (or ZnSnO) film conductivity at the HfLaO<sub>x</sub>/ZnO (or ZnSnO) interfaces is higher (or lower) than that at the SiO<sub>2</sub>/ZnO (or ZnSnO) interfaces, which is consistent with the result of the measured  $\mu^{t}_{FE}$  in Figure 6. The high-dielectric environment by the gate insulator is not the dominant factor that determine the  $\mu_{FE}$  in the channel (the dielectric constants of HfLaO<sub>x</sub> and SiO<sub>2</sub> are 22 and 3.9,<sup>[26]</sup> respectively), which has been known to decrease the Coulomb-scattering effects in a 2-dimensional semiconductor.[33] The root-mean-square surface roughness of SiO2 and HfLaOx are similar when measured by an atomic force microscope.[26] We may conclude that getting good interfaces for high- $\mu_{FF}$  values depends on OS film-growing procedures on top of the gate insulator surfaces during the solution processes.

#### 7. Conclusion

In conclusion, we investigated how  $C_i$  affects  $\mu_{FE}$  of the solution-processed OS TFTs. With the developed TFT model based on the MTR and VRH percolation mechanisms, we successfully verified that  $\mu_{FE}$  of the nanocrystalline ZnO and the amorhpous ZnSnO TFTs depends on the gate capacitances in the power-law dependence, which cannot be supported by the conventional MOSFETs theory. Also, the characteristics of the  $C_i$ -dependent  $\mu_{FE}$  of the fabricated OS TFTs are clearly and well explained by the single-piece analytical expression.  $\mu_{FE}$  of the ZnO TFTs which have the high-trap characteristic temperature strongly depends on  $C_i$  than that of the ZnSnO TFTs having the low-trap characteristic temperature. In particular, when the ZnO TFTs had different  $C_i$ , values from 13 to 203 nF cm $^{-2}$ , the measured  $\mu_{FE}$  dramatically

changed by  $\approx 100$  times from 0.066 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at  $C_i = 13 \text{ nF cm}^{-2} \text{ to } 6.01 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1} \text{ at}$  $C_i = 203 \text{ nF cm}^{-2}$  for a low-voltage operation  $(V_{GF} = 4 \text{ V})$ . The measured  $\mu_{FF}$  degradaed by the leakage current flowing from the gate to drain electrode, and the  $\mu_{FE}$  degradation was more notable for the devices with low  $C_i$  and high  $T_0$ . Without the leakage current, the  $\mu_{FE}$  of the ZnO and ZnSnO TFTs would have the scattering-limited maximum. Our findings can be the general guideline of the the  $C_{\mathrm{i}}$ -dependent  $\mu_{\mathrm{FE}}$  characteristics for TFTs based on disordered semiconductors with single exponential DOS for the localized states, like organic semiconductors[21] as well as solution-processed OSs. The proposed single-piece expression for the field-

effect mobility will be utilized to intuitively predict, design, and optimize solution-processed OS TFTs.

#### 8. Experimental Section

All TFTs were fabricated on heavily B-doped p-type Si wafer substrates with a 8-nm, (for TFTs with  $C_i > 100$  nF cm<sup>-2</sup>), 50-nm (for TFTs with  $C_i = 53 \text{ nF cm}^{-2}$ ), 100-nm (for TFTs with  $C_i = 33 \text{ nF cm}^{-2}$ ), and 200-nm (for TFTs with  $C_i = 13$  nF cm<sup>-2</sup>)-thick SiO<sub>2</sub> layer, which were sequentially washed with detergent, de-ionized water, acetone, and isopropyl alcohol and exposed to ultraviolet ozone for 30 min before depositing films. The substrates for each capacitor were equal to those of associated TFT devices. The HfLaOx layers were deposited onto the substrates by spin coating of mixed hafnium:lanthanum-precursor solution, which were prepared by a method described in ref. [26]. A thickness of the fabricated HfLaO<sub>x</sub> layer was varied from 45 nm to  $\approx$  90 nm, where the thickness was controlled by multiple spin-casting of the HfLaOx layer (the thickness of single HfLaOx layer with spin casting at 2000 rpm was  $\approx$  45 nm). A ZnO solution (which was prepared by dissolving 0.001 mole of zinc oxide (Sigma-Aldrich 99.999%) into 12 mL of ammonium hydroxide (aq) (Alfa Aesar, 99.9%)) or a ZnSnO solution (which was prepared by dissolving 0.15 M zinc acetate (Sigma Aldrich 99.99%), 0.225 м tin chloride (Sigma Aldrich 99.99%), an 0.15 M ethanolamine (Sigma Aldrich 99.5%) into 2-methoxyethanol) was spin coated onto the HfLaO<sub>x</sub>-coated substrates under ambient conditions. [6,8] The ZnO (or ZnSnO)-deposited substrates were then annealed at 300 °C (or 500 °C) for 1 h in ambient. Then, 100-nm-thick Al electrodes were deposited on all devices via thermal evaporation at 10<sup>-6</sup> Torr; the TFTs and capacitors were defined by the metal shadow masks.

The transfer characteristics for all the TFTs and the capacitance characteristics for all the capacitors were measured using an Agilent 4155B semiconductor parameter analyzer and Agilent 4284A precision LCR meter, respectively, at  $10^{-3}$  Torr in the dark. Cross-sectional images of the TFTs were obtained via a TEM (JEM-2100F, JEOL), and the specimens for TEM measurement were prepared using a focused ion beam instrument (NOVA 600 NanoLab, FEI Company).

#### **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

#### Acknowledgements

This work was supported by Basic Research Program (2011–0018113) funded by Korea Research Fund (NRF) and the Center for Advanced

ADVANCED FUNCTIONAL MATERIALS www.afm-journal.de

#### www.MaterialsViews.com

Soft-Electronics funded by the Ministry of Science, ICT and Future Planning as Global Frontier Project (2013M3A6A5073177). We also thank LG Display for the academy-industry bilateral collaboration program.

Received: February 19, 2014 Published online: April 24, 2014

- [1] R. H. Reuss, B. R. Chalamala, A. Moussessian, M. G. Kane, A. Kumar, D. C. Zhang, J. A. Rogers, M. Hatalis, D. Temple, G. Moddel, B. J. Eliasson, M. J. Estes, J. Junz, E. Handy, E. S. Harmon, D. B. Salzman, J. M. Woodall, M. A. Alam, J. Murthi, S. C. Jacobson, M. Olivier, D. Markus, P. M Cambell, E. Snow, *Proc. IEEE* 2005, 93, 1–18.

- [2] Y. Sun, J. A. Rogers, Adv. Mater. 2011, 10, 382-388.

- [3] M.-G. Kim, M. G. Kanatzidis, A. Facchetti, T. J. Marks, Nat. Mater. 2011. 10, 382–388.

- [4] K. K. Banger, Y. Yamashita, K. Mori, R. L. Peterson, T. Leedham, J. Rickard, H. Sirringhaus, Nat. Mater. 2011, 10, 45-50.

- [5] Y.-H. Kim, J.-S. Heo, T.-H. Kim, S. Park, M.-H. Yoon, J. Kim, M. S. Oh, G.-R. Yi, Y.-Y. Noh, S. K. Park, *Nature* 2012, 489, 128–132.

- [6] S. Y. Park, B. J. Kim, K. Kim, M. S. Kang, K.-H. Lim, T. I. Lee, J. M. Myong, H. K. Baik, J. H. Cho, Y. S. Kim, Adv. Mater. 2012, 24, 834–838

- [7] K. Kim, S. Y. Park, J.-B. Seon, K.-H. Lim, K. Char, J. Shin, Y. S. Kim, Adv. Funct. Mater. 2011, 21, 3546-3554.

- [8] K.-H. Lim, K. Kim, S. Kim, S. Y. Park, H. Kim, Y. S. Kim, Adv. Mater. 2013, 25, 2994–3001.

- [9] K. Kim, E. Lee, J. Kim, S. Y. Park, K.-H. Lim, C. Shin, Y. S. Kim, J. Mater. Chem. C 2013, 1, 7742–7748.

- [10] K. Kim, J. H. Park, Y. B. Yoo, S. Y. Park, K.-H. Lim, K. H. Lee, H. K. Baik, Y. S. Kim, J. Mater. Chem. C 2013, 1, 7166-7174.

- [11] B. N. Pal, B. M. Dhar, K. C. See, H. E. Kats, Nat. Mater. 2009, 8, 898–903.

- [12] J. Jang, R. Kitsomboonloha, S. L. Swisher, E. S. Park, H. Kang, V. Subramanian, Adv. Mater. 2013, 25, 1042–1047.

- [13] H. Bong, W. H. Lee, D. Y. Lee, B. J. Kim, J. H. Cho, K. Cho, Appl. Phys. Lett. 2010, 96, 192115.

- [14] S. M. Sze, K. K. Ng, Physics of Semiconductor Devices, Wiley, Hoboken, NJ, USA 2007.

- [15] P. Servati, A. Nathan, G. A. J. Amaratunga, Phys. Rev. B 2006, 74, 245210.

- [16] F. Torricelli, J. R. Meijboom, E. Smits, A. K. Tripathi, M. Ferroni, S. Federici, G. H. Gelinck, L. Colalongo, Z. M. Kovacs-Vajna, D. de Leeuw, E. Cantatore, *IEEE Trans. Electron. Devices* 2011, 58, 2610–2617.

- [17] V. Ambegaokar, B. I. Halperin, J. S. Langer, Phys. Rev. B 1971, 4, 2612–2620.

- [18] T. Kamiya, K. Nomura, H. Hosono, J. Disp. Tech. 2009, 5, 273-288.

- [19] A. Salleo, T. W. Chen, A. R. Volkel, Y. Wu, P. Liu, B. S. Ong, R. A. Street, *Phys. Rev. B* **2004**, *70*, 115311.

- [20] M. C. J. M. Vissenberg, M. Matters, Phys. Rev. B 1998, 57, 12964–12967.

- [21] H. Sirringhaus, Adv. Mater. 2005, 17, 2411-2425.

- [22] J. Robertson, Phys. Status Solidi 2008, 245, 1026-1032.

- [23] F. J. Garcia-Sanchez, A. Oritz-Conde, IEEE Trans. Electron. Devices 2012, 59, 46–50.

- [24] S. T. Meyers, J. T. Anderson, C. M. Hung, J. Thompson, J. F. Wager, D. A. Keszler, J. Am. Chem. Soc. 2008, 130, 17603–17609.

- [25] N. C. Su, S. J. Wang, A. Chin, Solid-State Lett. 2010, 13, H8-H11.

- [26] J. Ko, J. Kim, S. Y. Park, E. Lee, K. Kim, K.-H. Lim, Y. S. Kim, J. Mater. Chem. C 2014, 2, 1050–105.

- [27] D. Kang, H. Lim, C. Kim, I. Song, J. Park, Appl. Phys. Lett. 2007, 90, 192101.

- [28] H. S. Bae, S. Im, Thin Solid Films 2004, 469-470, 75-79.

- [29] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, H. Hosono, Nature 2004, 432, 488–492.

- [30] R. L. Hoffman, J. Appl. Phys. 2003, 95, 5813.

- [31] E. Fortunato, P. Barquinha, R. Matins, Adv. Mater. 2003, 24, 2945–2986.

- [32] Y. Natsume, H. Sakata, Thin Solid Films 2000, 372, 30-36.

- [33] D. Jena, A. Konar, Phys. Rev. Lett. 2007, 98, 136805.

Adv. Funct. Mater. 2014, 24, 4689-4697